#### АРХИТЕКТУРА КОМПЬЮТЕРНЫХ СИСТЕМ

**Лекция** 4: *Цифровой логический уровень*

### План лекции

- Вентили

- Интегральные схемы

- Организация памяти

# Уровни архитектуры

- Цифровой логический уровень

- Уровень микроархитектуры

- Уровень архитектуры набора команд

- Уровень операционной системы

- Уровень ассемблера

#### Вентили

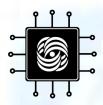

- (а) Транзисторный инвертор

- (b) Вентиль НЕ-И

- (с) Вентиль НЕ-ИЛИ

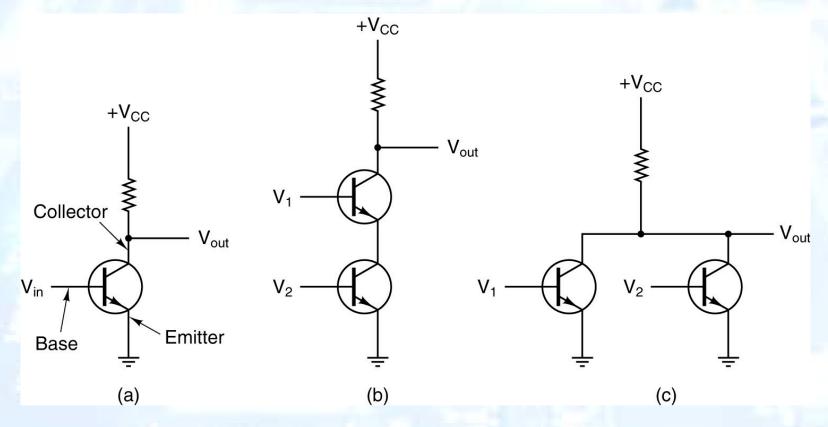

# Вентили и булева алгебра

# Булева алгебра

(k

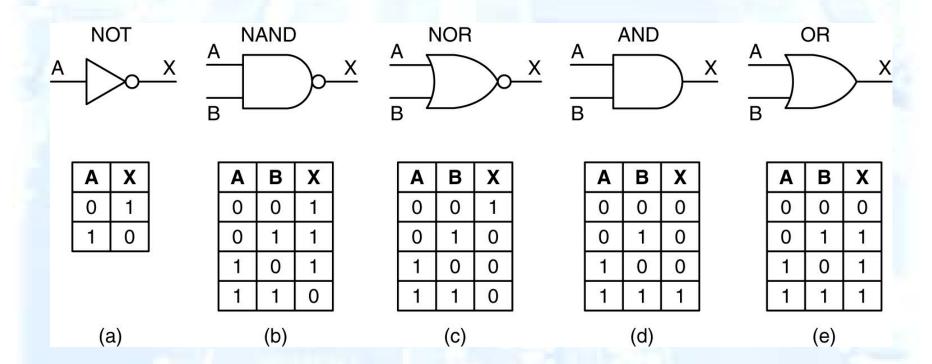

| Α | В | C | IVI |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 0   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 1   |

| 1 | 0 | 0 | 0   |

| 1 | 0 | 1 | 1   |

| 1 | 1 | 0 | 1   |

| 1 | 1 | 1 | 1   |

|   |   |   |     |

(a)

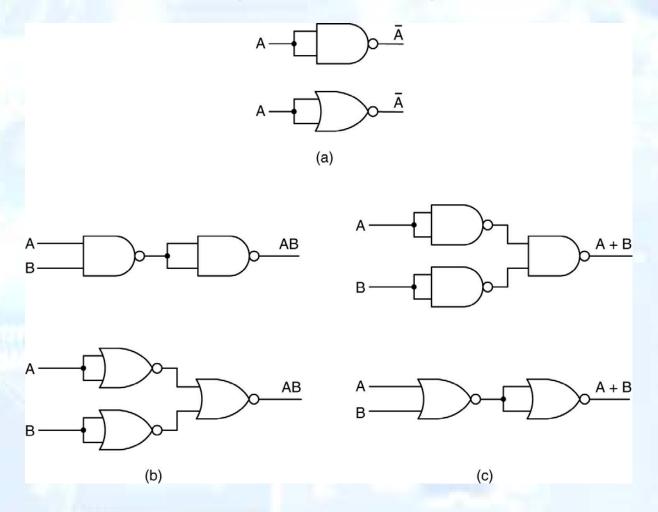

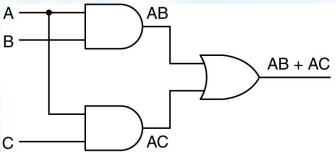

### Эквивалентность схем

# Эквивалентность схем (2)

| , |       |                          | 200000000                        | AB + AC                               |

|---|-------|--------------------------|----------------------------------|---------------------------------------|

| 0 | 0     | 0                        | 0                                | 0                                     |

| 0 | 1     | 0                        | 0                                | 0                                     |

| 1 | 0     | 0                        | 0                                | 0                                     |

| 1 | 1     | 0                        | 0                                | 0                                     |

| 0 | 0     | 0                        | 0                                | 0                                     |

| 0 | 1     | 0                        | 1                                | 1                                     |

| 1 | 0     | 1                        | 0                                | 1                                     |

| 1 | 1     | 1                        | 1                                | 1                                     |

|   | 1 1 0 | 1 0<br>1 1<br>0 0<br>0 1 | 1 0 0<br>1 1 0<br>0 0 0<br>0 1 0 | 1 0 0 0   1 1 0 0   0 0 0 0   0 1 0 1 |

(a)

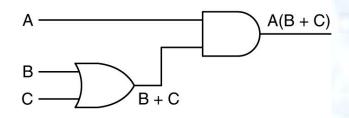

| Α | В | С | Α | B+C | A(B + C) |

|---|---|---|---|-----|----------|

| 0 | 0 | 0 | 0 | 0   | 0        |

| 0 | 0 | 1 | 0 | 1   | 0        |

| 0 | 1 | 0 | 0 | 1   | 0        |

| 0 | 1 | 1 | 0 | 1   | 0        |

| 1 | 0 | 0 | 1 | 0   | 0        |

| 1 | 0 | 1 | 1 | 1   | 1        |

| 1 | 1 | 0 | 1 | 1   | 1        |

| 1 | 1 | 1 | 1 | 1   | 1        |

|   |   |   |   |     |          |

(b)

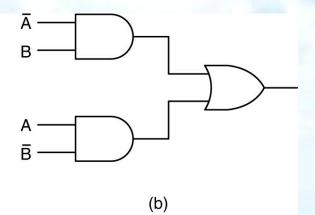

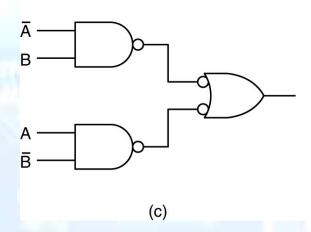

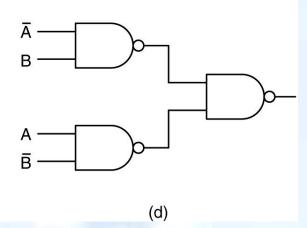

# Реализация XOR

| Α   | В | XOR |  |  |

|-----|---|-----|--|--|

| 0   | 0 | 0   |  |  |

| 0   | 1 | 1   |  |  |

| 1   | 0 | 1   |  |  |

| 1   | 1 | 0   |  |  |

| (a) |   |     |  |  |

# Электрические характеристики

| Α              | В              | F              |

|----------------|----------------|----------------|

| 0              | OV             | 0              |

| 0              | 5 <sup>V</sup> | 0              |

| 5 <sup>V</sup> | 0^             | 0              |

| 5 <sup>V</sup> | 5 <sup>V</sup> | 5 <sup>V</sup> |

| Α | В | F |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Α | В | F |

|---|---|---|

| 1 | 1 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 0 | 0 | 0 |

(a)

(b)

(c)

- (а) Электрические характеристики устройств.

- (b) Позитивная логика.

- (с) Негативная логика.

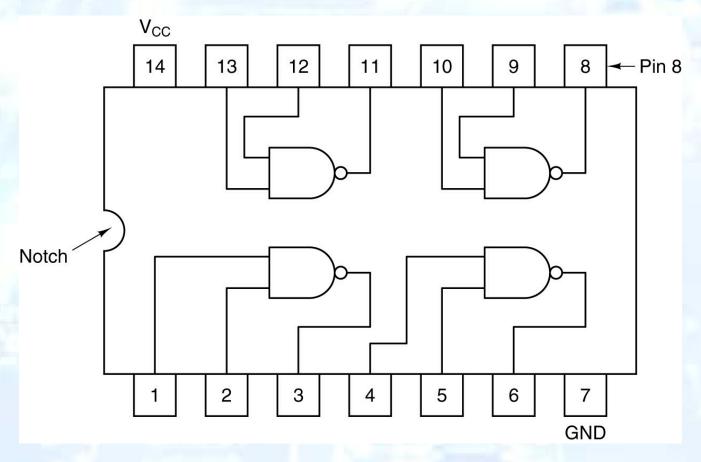

## Интегральные схемы

# Основные интегральные схемы

- Комбинаторные схемы

- Арифметические схемы

- Тактовые генераторы

### Комбинаторные схемы

- Мультиплексоры

- Декодеры

- Компараторы

- Программируемые логические матрицы

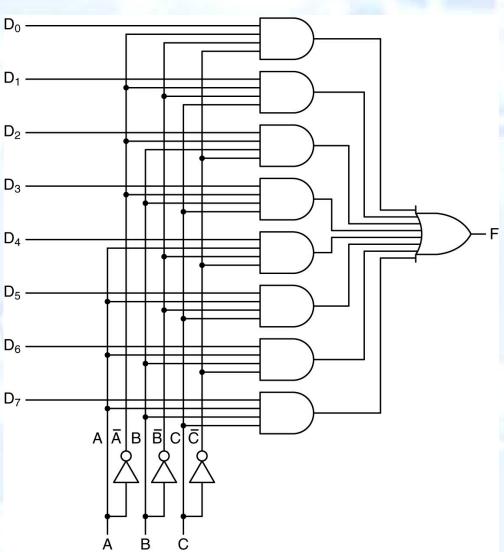

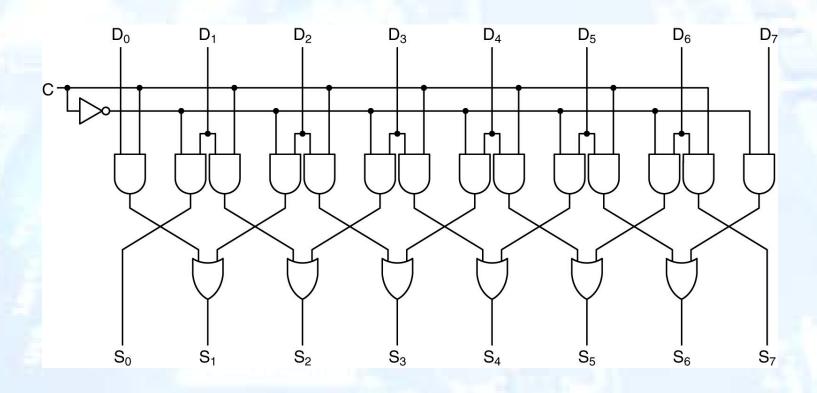

### Мультиплексор

- Вход 2^N

- Выход 1

- N линий управления

- Выбранный вход соединяется с выходом

# Мультиплексоры (2)

8-ми входовый мультиплексор

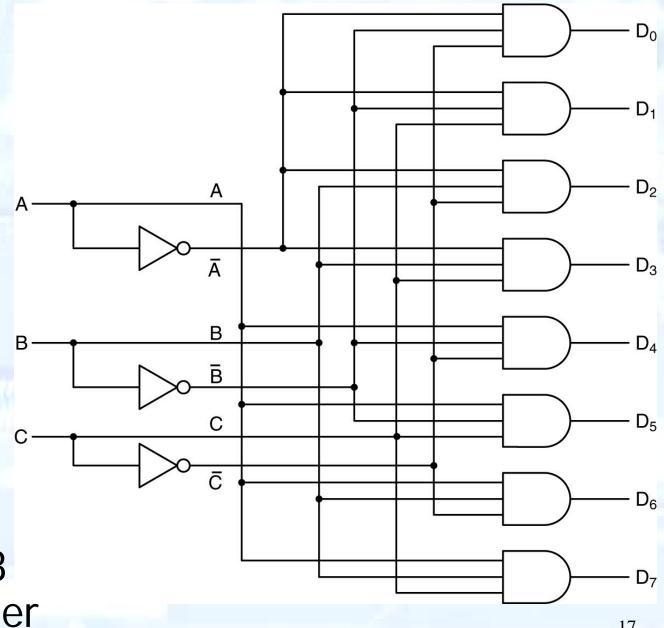

### Декодеры

- Вход n-разрядное число

- Выход '1' одна из 2^N выходных линий

# Декодер

A 3-to-8 decoder

17

circuit

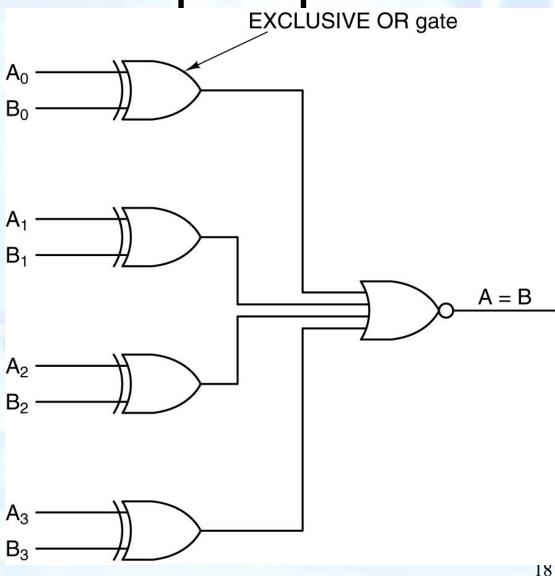

Компараторы

Простой 4битный компаратор

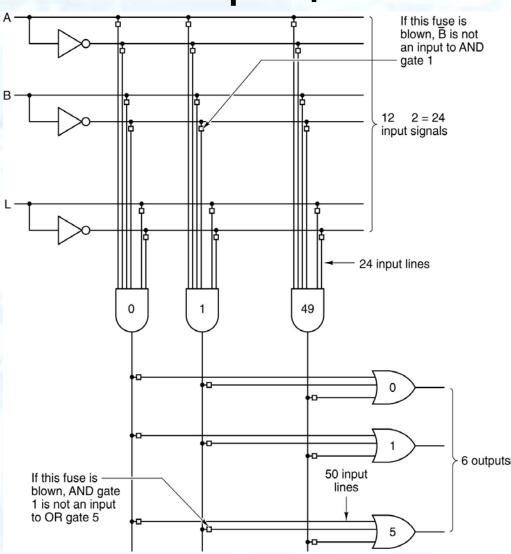

# Программируемые Логические Матрицы

12-входов, 6-выходов Программируемая логическая матрица.

Содержит плавкие перемычки.

### Арифметические схемы

- Схемы сдвига

- Сумматоры

- Арифметико-логические устройства

### Схемы сдвига

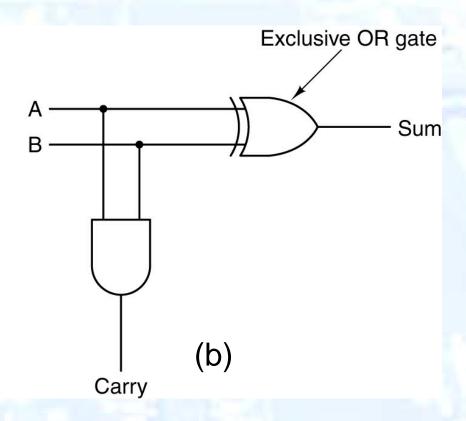

### Полусумматор

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 0   | 1     |

(a)

- (а) Таблица истинности для 1 бита.

- (b) Схема полусумматора.

22

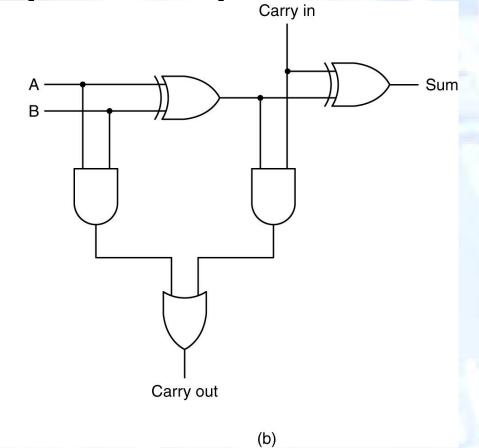

### Сумматор

| Α | В | Carry<br>in | Sum | Carry<br>out |

|---|---|-------------|-----|--------------|

| 0 | 0 | 0           | 0   | 0            |

| 0 | 0 | 1           | 1   | 0            |

| 0 | 1 | 0           | 1   | 0            |

| 0 | 1 | 1           | 0   | 1            |

| 1 | 0 | 0           | 1   | 0            |

| 1 | 0 | 1           | 0   | 1            |

| 1 | 1 | 0           | 0   | 1            |

| 1 | 1 | 1           | 1   | 1            |

- (a)

- (а) Таблица истинности для сумматора.

- (b) Схема истинности

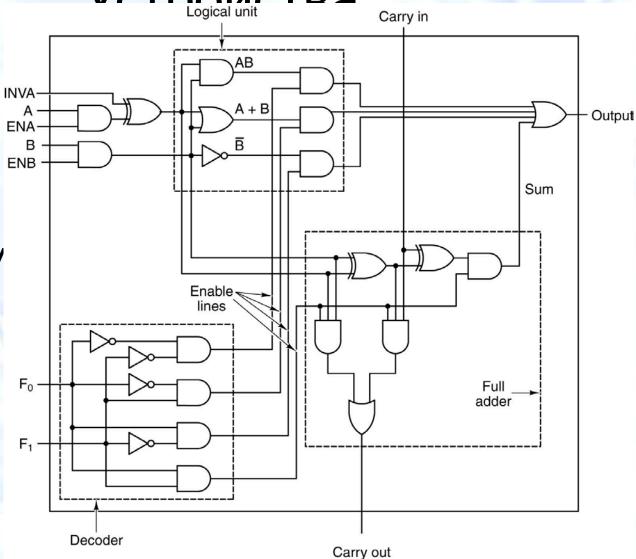

### Арифметико-Логические

# VCTDOIACTD 2

1-битовое АЛУ

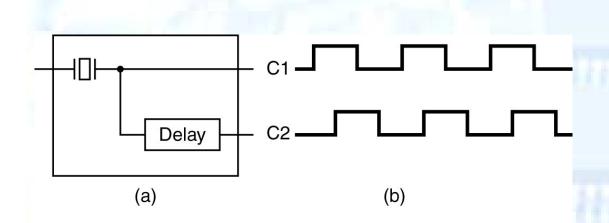

### Тактовые генераторы

- (а) Тактовый генератор

- (b) Временная диаграмма

- (с) Генерация асинхронных импульсов

#### Память

- Защёлки

- Синхронные SR-Защёлки

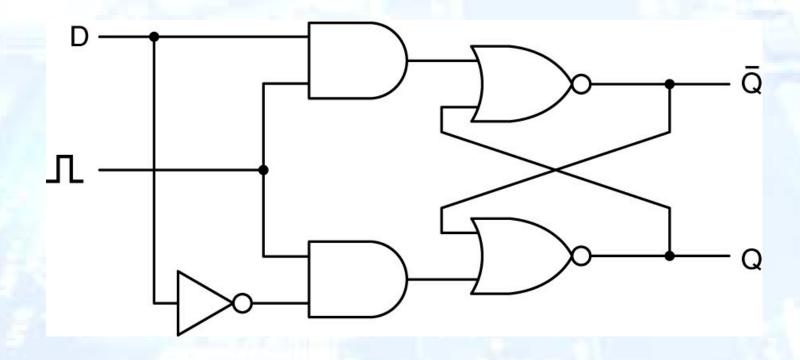

- Синхронные D-Защёлки

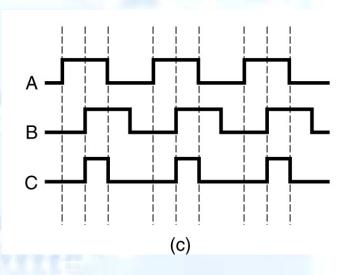

# Защёлки

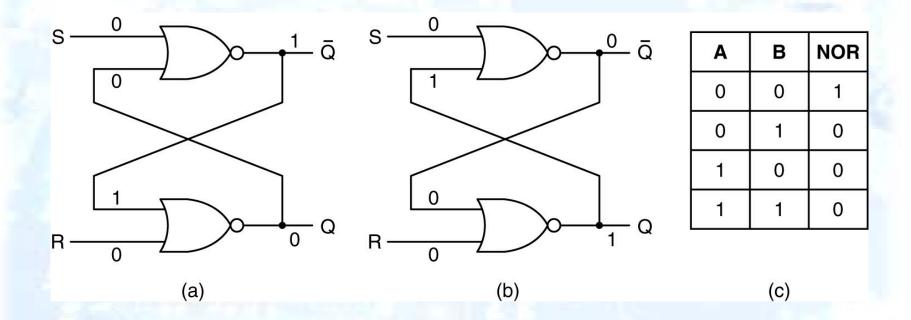

# Синхронные SR-защёлки

# Синхронные D-защёлки

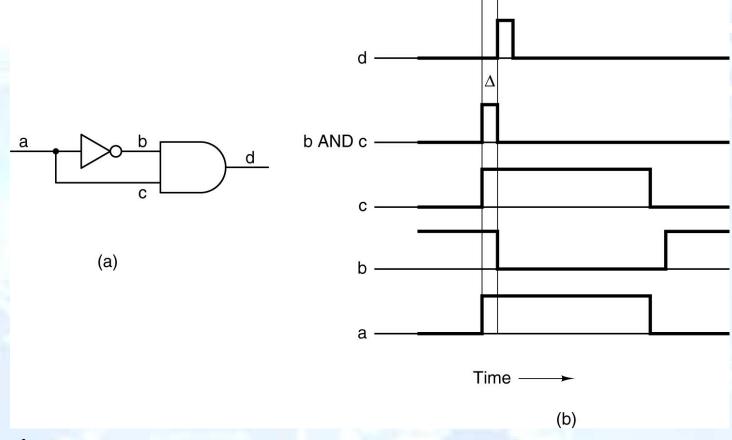

### Триггеры

- (а) Генератор импульса

- (b) Временная диаграмма для 4 точек <sub>30</sub> на схеме.

# Спасибо за внимание!